posted by Walrusful

on Sun, 2016-05-08 21:48

In-game name:

Walrusful

Age (Optional):

12

Why are you interested in joining this server?:

I am interested in join this server to expand my knowledge of redstone and computers. I hope the teachers here will be active and supportive.

Current Redstone knowledge:

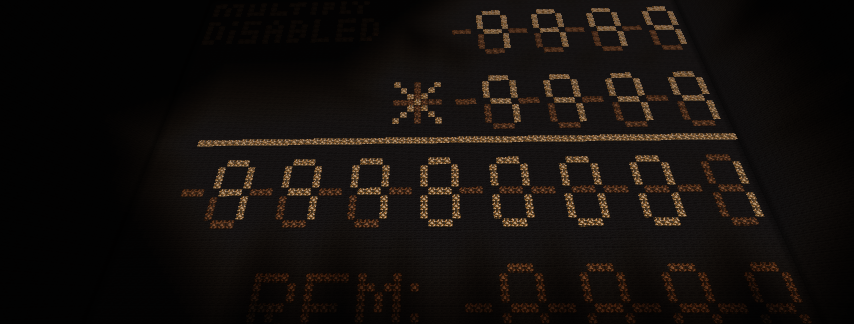

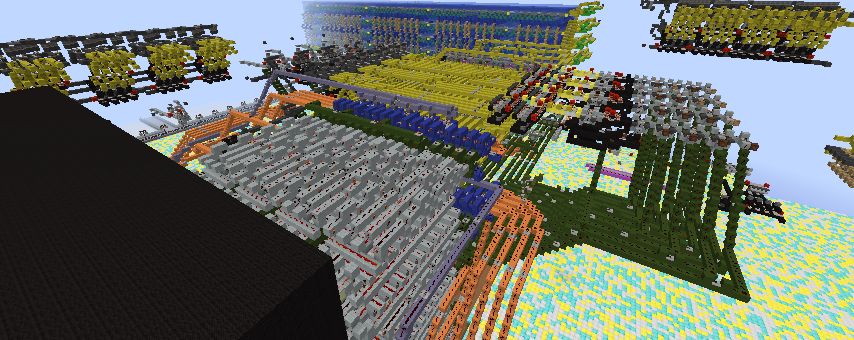

Computing, Binary, Logical Gates, Adders, Subtractors, Dividers, Multipliers, Ica, cca, rca, cle, cla, Alus, Cpus, Mux, Demux, Truth Tables, Shifters, Binary coded decimal, instruction sets, risc, cisc, barrel shifters, Memory, Rom, Ram, 7-segment displays, Fixed length arithmetic and complements, Latches, flip-flops, Basic boolean algebra, The difference between sequential and combinational logic, Decoder, Encoder, Data flip flop (DFF) and registers, Clocks and monostables, Binary counter, Serial register, Binary comparators, Program counter, Finite state machine, The difference between sequential and combinational logic, Big O Notation, Analysis of the addition algorithm, and how to build a display that shows a banana.

Past Redstone Experience:

List of a Redstone Creation I have Made.

1.

RISC-16 CPU:

IS:

Mnemonic Name and

Format

Opcode

(binary)

Assembly

Format Action

add Add

RRR-type 000 add rA, rB, rC Add contents of regB with regC,

store result in regA.

addi Add Immediate

RRI-type 001 addi rA, rB, imm Add contents of regB with imm,

store result in regA.

nand Nand

RRR-type 010 nand rA, rB, rC Nand contents of regB with regC,

store results in regA.

lui

Load Upper

Immediate

RI-type

011 lui rA, imm

Place the 10 ten bits of the 16-bit imm

into the 10 ten bits of regA, setting the

bottom 6 bits of regA to zero.

sw

Store Word

RRI-type 101 sw rA, rB, imm

Store value from regA into memory.

Memory address is formed by adding

imm with contents of regB.

lw Load Word

RRI-type 100 lw rA, rB, imm

Load value from memory into regA.

Memory address is formed by adding

imm with contents of regB.

beq Branch If Equal

RRI-type 110 beq rA, rB, imm

If the contents of regA and regB are the

same, branch to the address

PC+1+imm, where PC is the address of

the beq instruction.

jalr

Jump And Link

Register

RRI-type

111 jalr rA, rB

Branch to the address in regB.

Store PC+1 into regA, where PC is the

address of the jalr instruction.

Specs:

The RiSC-16 is an 8-register, 16-bit computer.

RiSC-16 Assembly Language and Assembler:

label:<whitespace>opcode<whitespace>field0, field1, field2<whitespace># comments

add regA, regB, regC R[regA] <- R[regB] + R[regC]

addi regA, regB, immed R[regA] <- R[regB] + immed

nand regA, regB, regC R[regA] <- ~(R[regB] & R[regC])

lui regA, immed R[regA] <- immed & 0xffc0

sw regA, regB, immed R[regA] -> Mem[ R[regB] + immed ]

lw regA, regB, immed R[regA] <- Mem[ R[regB] + immed ]

beq regA, regB, immed

if ( R[regA] == R[regB] ) {

PC <- PC + 1 + immed

(if label, PC <- label)

}

jalr regA, regB PC <- R[regB], R[regA] <- PC + 1

lw 1,0,count # load reg1 with 5 (uses symbolic address)

lw 2,1,2 # load reg2 with -1 (uses numeric address)

start: add 1,1,2 # decrement reg1 -- could have been addi 1,1,-1

beq 0,1,1 # goto end of program when reg1==0

beq 0,0,start # go back to the beginning of the loop

done: halt # end of program

count: .fill 5

neg1: .fill -1

startAddr: .fill start # will contain the address of start (2)

About how often do you play Minecraft?:

1-5 hours per day

Anything else you'd like to mention? (Optional):

I like redstone :P

Application status:

Approved