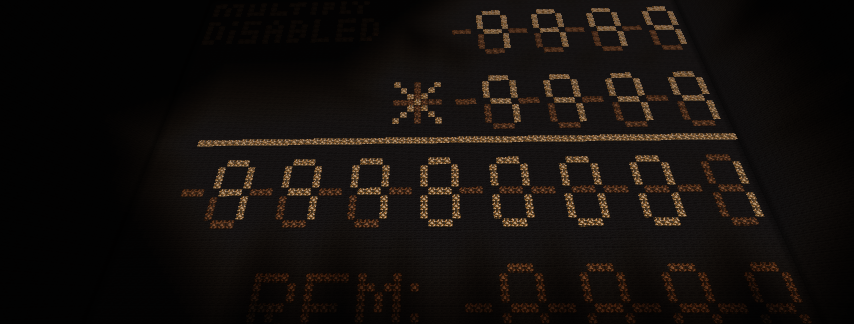

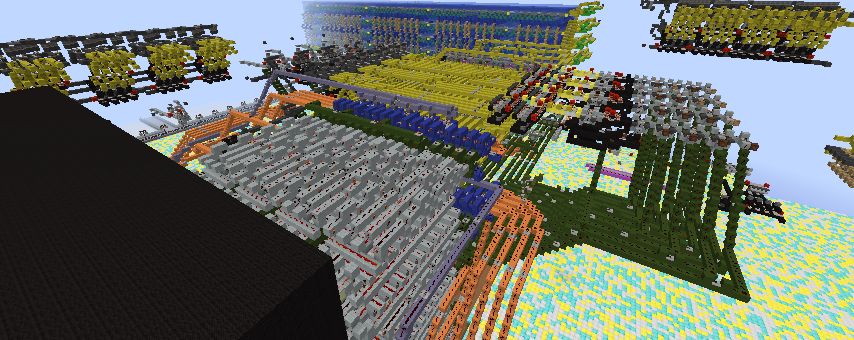

My machine is a CPU that has been coded to calculate Fibonacci numbers. It has an ALU that can do all Boolean functions and add/subtract. It's instructions are coded into the read only memory. It goes through a loop of steps to calculate the Fibonacci numbers. When the output is too large for the bit width, the CPU starts over again from the beginning. In order to calculate the Fibonacci numbers, here is what the CPU does: First, it sets both RAM slots to one. Then it repeats the following process: It adds the two numbers and sets them to RAM slot one. Then it does it again, but this time setting it to RAM slot two. It sets the n-1 value in the slot where the old n-2 value was each time. Every time a new Fibonacci number is calculated, it is sent to the display. After the Fibonacci number grows out of the bit width, it restarts.

Hit the clock lever. Watch the Fibonacci numbers appear on the board.

Comments

Reason for Denial

Hello, BusinessWither!

At this time, I have decided to deny your promotion request. Whilst the build is quite promising, there are some substantial improvements I would like to see made.

Firstly, the build looks to be fairly original and it did indeed run Fibonacci quite well. I was quite pleased to see this, it is always nice to see builds that work as intended. My biggest issues are lack of features and some questionable design choices, which I will outline below.

The CPU does not have a proper program counter (PC). As it currently stands, it looks as though the next line of the program is always hard coded into the ROM. This may work fine for Fibonacci, but can become limiting for other programs. What I would like to see instead is a proper PC which counts on its own and can perform conditional and unconditional branching/jumps. This is a crucial portion to include in a CPU to demonstrate your understanding of computing theory and redstone logic.

Certain operations of the ALU seem "hacky." For example, AND, OR, and XOR have all been "separated" from the adder. While it works in theory (I have not validated its functionality), it is larger and possibly slower than necessary, and does not demonstrate thorough knowledge of ALUs. Instead, there are ways to manipulate the adder itself to achieve these functions. For example, for XOR you could simply disable the carry lines, and the adder itself would then be performing bitwise XOR. My explanation may be a bit confusing so feel free to ask other members or myself for help!

There is no control unit (CU). While this is not a huge issue, I figured I would mention it, since it is usually a nice thing to have. If you're unsure what this is, again feel free to reach out to myself or the community for help!

Finally, there's some weird stuff going on with the display. It looks as though it is only built to be able to display Fibonacci, as some of the outputs don't appear to be wired in. There is also a major inefficiency in your display design when converting the binary output. You first convert the binary output to individual outputs with a binary decoder, then you encode it to signal strength, then you once again decode the signal strength to individual outputs. Instead, you could just use the individual lines right out of the decoder and skip the SS step all together.

Overall, I am pleased to see your interest in ranking up and I have high hopes for you. It seems as though you are on the right track and I would love to see you improve with this feedback and hopefully learn something useful along the way.

Happy Redstoning!

- Farex