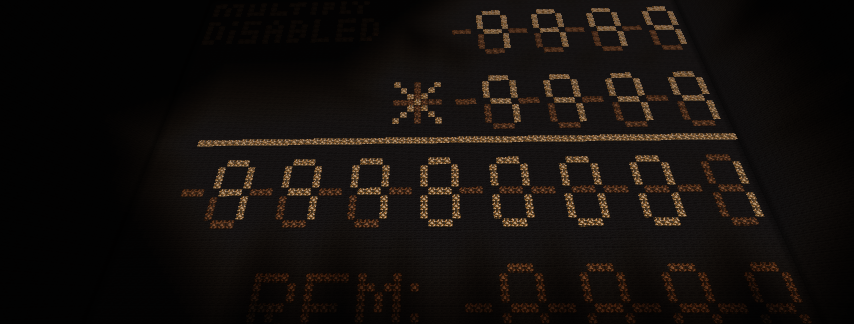

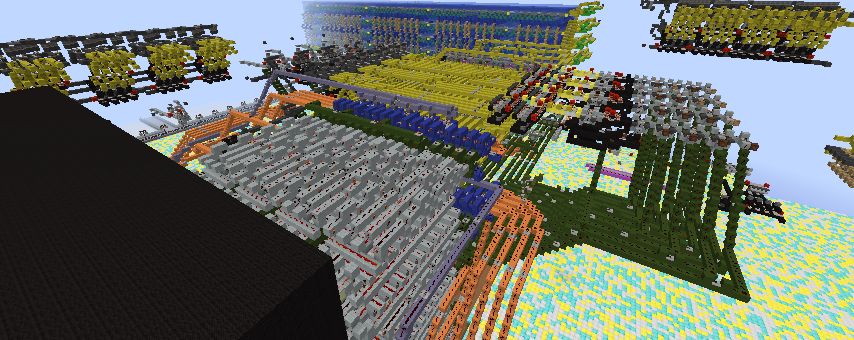

my machine is a 8 bit arithmitic logic unit that uses a instant carry adder. it can preform the following operations: addition, subtraction, or, and, nand, xor, nor, xnor. icas work by having one long carry line with no restriction which allows the carry to happen instantly

instructions: for addition: do nothing just input your prefered numbers to add. subtraction: invert b and carry in. or: activate or flag. xor: or flag and flood carry. xnor: invert b activate or and flood carry. and: invert a and b activate or and flood carry. nand: invert a and b then activate or.

Comments

a thanks to the reviewer

thank you for considering my application. if you are going to deny it can you please explain why in a comment so i can improve.

-WhatsTaters6214

Denied

The ICA is looking decent.

Things are labeled too.

Carry over the whole width works!

There had been some blocks with inverters missing - stacked that for you. (In the bottom inverter).

For the next rank Regular, we normally expect something on the level of a whole (quite simple) CPU.

Just one ALU is too simple, hence I will deny your PR.

BUT:

An ALU like yours (with opcode deocder) is something that you can pass the /trial with!

So if you rebuild this ICA ALU with an opcode decoder in the /trial - you will pretty surely pass the trial :)

Then you are Learner+ which has no less features than a Regular.

Which gives you WE + Plot.

thank you for your feed back

first of all i completly understand the reason of denial. secondly i was aiming for tinker not regular. and finnaly a appriciate the feedback thabk you!